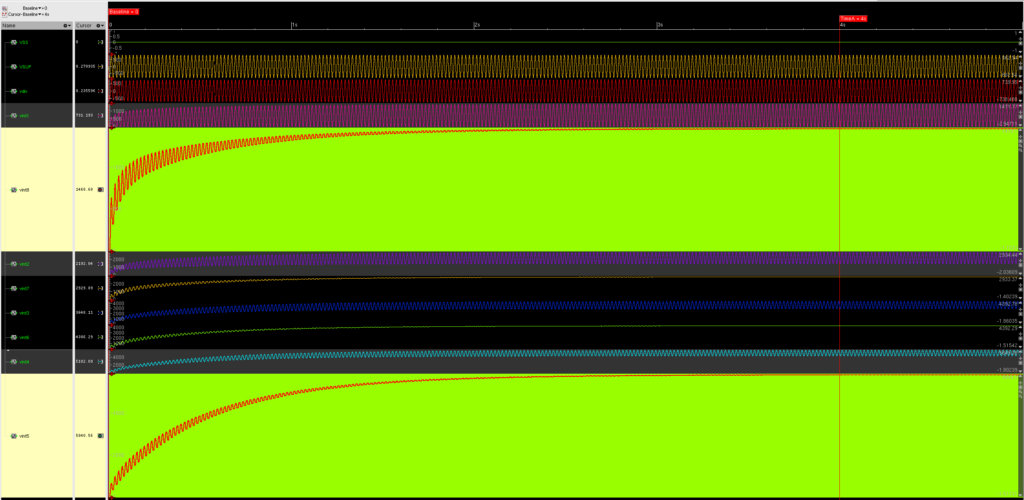

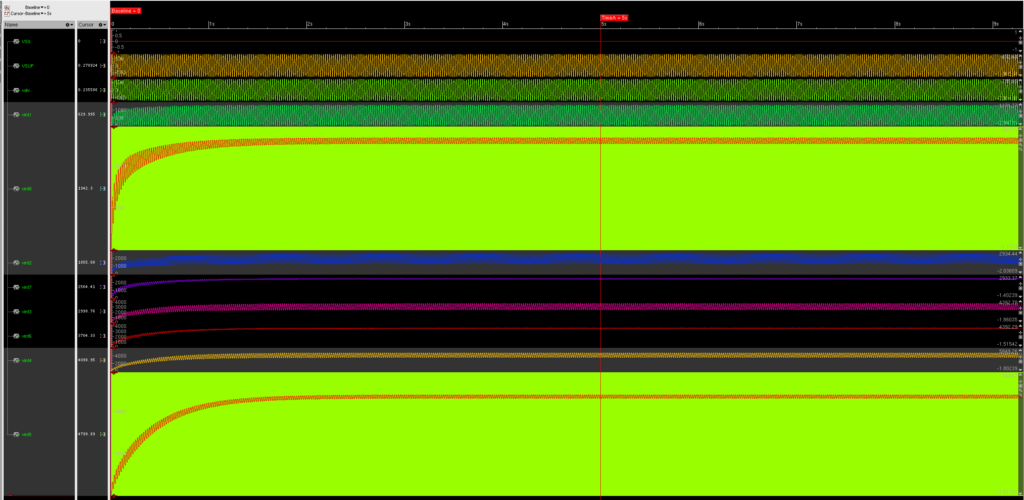

Here is a verilog-AMS model. Results are very sensitive to reverse (leakage) current of diodes (15nA simulated here).

With one leaky cell bass (500MOhm), sensitivity changes: -0.8dB on treble, -1.7dB on bass.

With one very leaky cell bass (250MOhm): 1270/4100V (-1.3dB/-3dB).

`include "timescale.sv"

module testbench();

interconnect VSUP;

interconnect VSS;

supplyAC #(.peak(610.0*1.414)) supply_VSUP (VSUP,VSS); // 610.0 28.1

interconnect vdiv;

interconnect vint1, vint2, vint3, vint4;

interconnect vint8, vint7, vint6, vint5;

interconnect vTreble, vBass;

localparam real p_set_init = 1.0;

resistor #(.p_res(330e3)) res1 (VSUP ,vdiv );

resistor #(.p_res(2.2e6)) res2 (vdiv ,VSS );

capacitor #(.p_cap(10e-9), .init( -750*p_set_init)) capa1(vdiv ,vint1);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa2(vint1,vint2);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa3(vint2,vint3);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa4(vint3,vint4);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa5(vint6,vint5);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa6(vint7,vint6);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa7(vint8,vint7);

capacitor #(.p_cap(10e-9), .init(-1500*p_set_init)) capa8(VSS ,vint8);

diode dio1(VSS ,vint1);

diode dio2(vint1,vint8);

diode dio3(vint8,vint2);

diode dio4(vint2,vint7);

diode dio5(vint7,vint3);

diode dio6(vint3,vint6);

diode dio7(vint6,vint4);

diode dio8(vint4,vint5);

localparam real nBass=2;

neon_kit #(.p_cap( 100e-9), .init(80.0*0.9*p_set_init)) neonT(vint8,vTreble);

neon_kit #(.p_cap( 390e-9), .init(80.0*0.9*p_set_init)) neonB(vint5,vBass ); // https://www.mouser.fr/Passive-Components/Capacitors/Film-Capacitors/_/N-9x371Z1yzvvqx?P=1z0z7l5Z1yzs9nvZ1y98vjeZ1yznbzrZ1z0vn48Z1z0wq34&FS=True

generate

capacitor #(.p_cap(1437e-12 ), .init(1500*p_set_init)) capaT(vTreble, VSS); // 1437pf 1200pF

if (1) begin

capacitor #(.p_cap( 770e-12*nBass), .init(6000*p_set_init)) capaB(vBass , VSS); // 770pF 1600pF

end

else begin

esl57_bass #(.nBass(nBass)) esl57_bass(vBass, VSS);

end

endgenerate

/*

Expectations for blink:

measured 6s for 1 bass cell only, 23GOhm, with 100pF

measured 0.4s for probe 1GOhm + 2 bass cells

Note: diaphragm conductivity is: 2 x 10^9 to 1 x 10^12 ohms per unit square

*/

localparam loadSelTreble = 3;

//

generate

if (loadSelTreble==1) resistor #(.p_res(100.0e9 )) resLeakTreble (vTreble ,VSS );

if (loadSelTreble==2) resistor #(.p_res(15.00e9 )) resLeakTreble (vTreble ,VSS ); // Standard treble cell

if (loadSelTreble==3) resistor #(.p_res( 5.00e9 )) resLeakTreble (vTreble ,VSS );

endgenerate

localparam loadSelBass = 3;

//

generate

if (loadSelBass ==1) resistor #(.p_res(100.0e9/nBass)) resLeakBass (vBass ,VSS );

if (loadSelBass ==2) resistor #(.p_res( 20.0e9/nBass)) resLeakBass (vBass ,VSS ); // Standard bass cell x2

if (loadSelBass ==3) resistor #(.p_res( 10.0e9/nBass)) resLeakBass (vBass ,VSS ); //

if (loadSelBass ==4) resistor #(.p_res( 1.00e9 )) resLeakBass (vBass ,VSS ); // EHT probe

if (loadSelBass ==5) resistor #(.p_res( 0.50e9 )) resLeakBass (vBass ,VSS ); // Leaky bass cell

if (loadSelBass ==6) resistor #(.p_res( 0.25e9 )) resLeakBass (vBass ,VSS ); // Very leaky bass cell

if (loadSelBass ==7) resistor #(.p_res( 0.01e9 )) resLeakBass (vBass ,VSS ); // Multimeter

endgenerate

endmodule

`include "timescale.sv"

module neon_kit (n1,n2);

inout n1,n2;

interconnect n1,n2, n_12;

parameter real p_cap = 100e-9;

parameter real init = 0.0;

resistor #(.p_res(10e6)) res(n1,n_12);

neon neon(n_12,n2); // n_12

capacitor #(.p_cap(p_cap), .init(init)) capa(n_12,n2); // n_12

//resistor #(.res(9e9)) resl(n_12,n2); // Leak through capacitor

endmodule

`include "constants.vams"

`include "disciplines.vams"

module neon (n1,n2);

electrical n1,n2;

real vNeon;

real iNeon;

real aClamp;

integer blink;

analog begin

aClamp=(abs(V(n1,n2))/80);

if (aClamp>=1)

I(n1,n2) <+ V(n1,n2)/300e3;

else if (aClamp>=0.9)

I(n1,n2) <+ V(n1,n2)/(300e3*((aClamp-0.9)/(1.0-0.9))+(1-(aClamp-0.9)/(1.0-0.9))*300e4); // smooth start

else if ((aClamp>=0.72) && (abs(I(n1,n2))>0))

I(n1,n2) <+ V(n1,n2)/300e4; // hysteresis

else

I(n1,n2) <+ 0;

//

vNeon = V(n1,n2);

iNeon = I(n1,n2);

if (abs(I(n1,n2))>0) blink=1; else blink=0;

end

endmodule

`include "disciplines.vams"

`include "timescale.sv"

module diode(n1,n2);

electrical n1,n2;

parameter real irev = 0.015e-6; // A (https://www.mouser.fr/datasheet/2/427/gp0220-1768061.pdf)

parameter real Vth = 0.26; // V

analog begin

I(n1,n2) <+ irev * (exp(V(n1,n2)/Vth) - 1.0);

end

endmodule

`include "constants.vams"

`include "disciplines.vams"

`include "timescale.sv"

module capacitor (vio,vss);

electrical vio,vss;

parameter real p_cap=1p exclude 0;

parameter real res=0.001;

parameter real init=0;

real vCapa;

analog begin

V(vio,vss) <+ idt(I(vio,vss))/p_cap+init + res*I(vio,vss); // neglectable resistor to break a loop

//

vCapa = V(vio,vss);

end

endmodule

`include "constants.vams"

`include "disciplines.vams"

`include "timescale.sv"

module resistor (vio,vss);

electrical vio,vss;

parameter real p_res=1 exclude 0;

analog begin

V(vio,vss) <+ p_res*I(vio,vss);

end

endmodule

`include "disciplines.vams"

`include "timescale.sv"

module supplyAC(n1,n2);

electrical n1,n2;

parameter real peak = 1.0;

parameter real res = 0.001; // resistor

parameter real freq = 50.0;

//

real phase = `M_PI/2.0;

real incr = 2.0 * `M_PI * freq * 10e-6; // 10us

always begin

#1 phase = phase + incr;

end

//

electrical gnd; ground gnd;

analog begin

V(n1,gnd) <+ peak * cos(phase) + res*I(n1,gnd);

V(n2,gnd) <+ 0.0;

end

endmodule

![]()